Frustrated with security issues in your code?

Find adding security too costly and slow?

Hate bugs that find you and not vice versa?

Are you a software engineer who’s interested in trialling and challenging a new technique that stops buffer overflows and other memory-safety issues — even in C or C++?

Come to this future tech talks and networking event to discover:

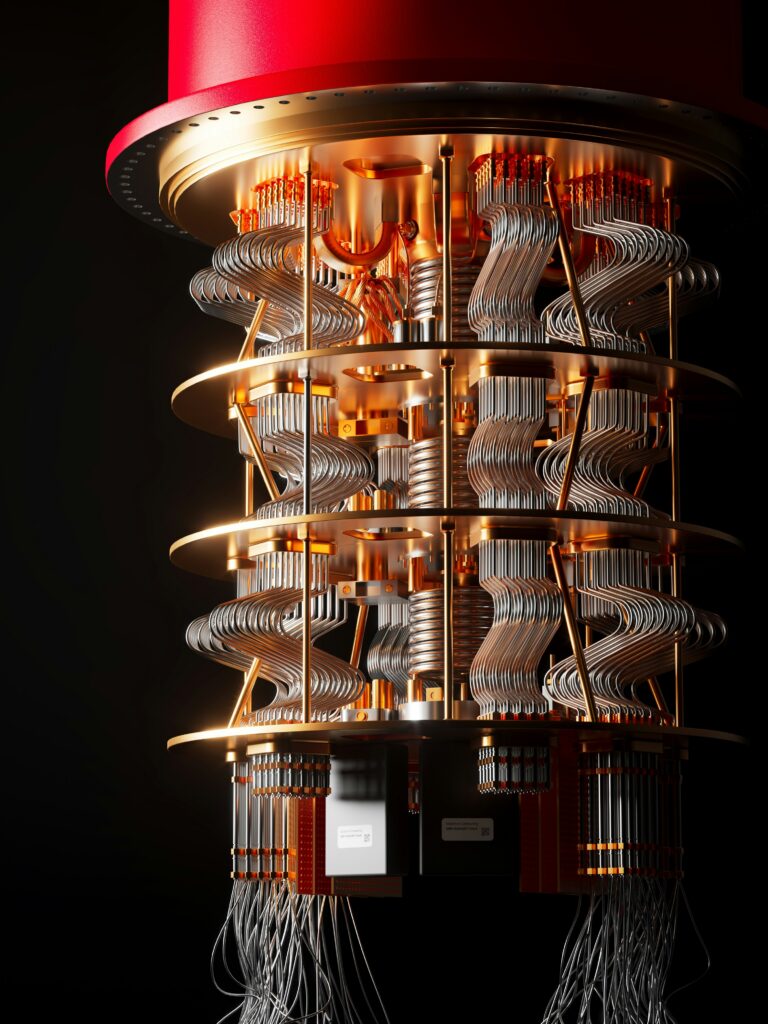

- Cambridge University’s new CHERI architecture: Capability Hardware Enhanced RISC Instructions.

- Why Arm partnered with University of Cambridge to develop prototype silicon.

- How you can use this prototype — the Arm Morello Board — to find bugs and memory safety issues.

- How you can get hold of a Morello board plus £15,000 funding to trial the Morello prototype architecture in your organisation.

During the event you’ll have the opportunity to talk to the designers and ask questions about this new technology.